type

status

date

slug

summary

tags

category

icon

password

牛客网刷题学习:语法注意:关于时序关于reg关于赋值关于case和if产生锁存器关于Testbench Tips关于奇校验和偶校验FPGA——quartus的报错Error: Can't compile duplicate declarations of entity "**" into library "work"的错误模板计数器模板SPISPI的模式模式0 (CPOL=0; CPHA=0)模式1 (CPOL=0; CPHA=1)模式2 (CPOL=1; CPHA=0)模式3 (CPOL=1; CPHA=1)Modelsim的注意

牛客网刷题学习:

语法注意:

1.module里定义时自动为wire型变量

2.always的@内变量设置为*可以自动匹配输入

3.always模块内被赋值的变量必须是reg型,赋的值类型随意

4.assign时被赋值的变量必须是wire型,赋的值类型随意

关于时序

在使用Verilog模块实现功能时,首先需要明确哪些操作是同时发生的,哪些是顺序发生的。三个例子中使用了"assign"语句、实例元件和"always"块,这三个例子描述的逻辑功能都是同时执行的。换句话说,即使将这三项写入同一个Verilog模块文件中,它们的书写顺序也不会影响最终的逻辑功能实现。这三项是并发执行的。

然而,在"always"模块内部,逻辑是按照特定顺序执行的。"always"块中的语句被称为"顺序语句",因为它们需要按顺序执行。值得注意的是,虽然多个"always"模块之间是同时执行的,但每个模块内部的语句都是顺序执行的。观察"always"内的语句就能理解其功能实现方式。比如if...else语句必须按顺序执行,否则就失去了意义。如果else语句在if语句之前执行,就无法达到预期的功能要求。因此,"always"模块内部的语句会严格按照书写顺序执行。

关于reg

1、reg类型数据的缺省初始值为不定值,x。

2、在“always”块内被赋值的每一个信号都必须定义成reg型。常代表触发器

3、但当一个reg型数据是一个表达式中的操作数时,它的值被当作是无符号值,即正值。例如:当一个四位的寄存器用作表达式中的操作数时,如果开始寄存器被赋以值-1,则在表达式中进行运算时,其值被认为是+15。

关于赋值

(1).非阻塞(Non_Blocking)赋值方式( 如 b <= a; )

- 块结束后才完成赋值操作。

- b的值并不是立刻就改变的。

- 这是一种比较常用的赋值方法。(特别在编写可综合模块时)

(2).阻塞(Blocking)赋值方式( 如 b = a; )

- 赋值语句执行完后,块才结束。

- b的值在赋值语句执行完后立刻就改变的。

- 可能会产生意想不到的结果。

关于case和if产生锁存器

避免偶然生成锁存器的错误。如果用到if语句,最好写上else项。如果用case语句,最好写上default项。遵循上面两条原则,就可以避免发生这种错误,使设计者更加明确设计目标,同时也增强了Verilog程序的可读性。

如果没有写就会保持原来的值,也就是产生了锁存器

关于Testbench Tips

1.testbench里需要根据Verilog里的输入输出重新定义变量,再实例化设计模块

2.initial作为初始化模块,被初始化的变量必须是reg型

关于奇校验和偶校验

奇校验用异或 奇数个1为1 ,偶数个为0

A = 4'b1010 ;

^A ; //结果为 1 ^ 0 ^ 1 ^ 0 = 1'b0

FPGA——quartus的报错

Error: Can't compile duplicate declarations of entity "**" into library "work"的错误

解决:

同一个文件名只能代表一个模块,即 *.v文件和 *.bdf文件等不同扩展名的文件只能代表同一个模块,如果建立了其中一个改扩展名的文件就不能建立统一名称的其他扩展名的文件。

模板

计数器模板

模板一

SPI

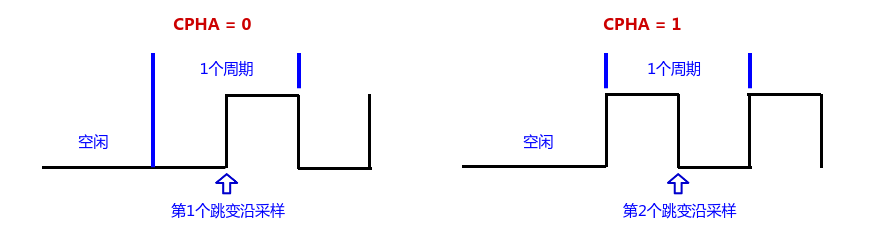

SPI的模式

模式 | CPOL | CPHA | 描述 |

0 | 0 | 0 | 时钟空闲时为低电平,数据在上升沿采样,下降沿输出。 |

1 | 0 | 1 | 时钟空闲时为低电平,数据在下降沿采样,上升沿输出。 |

2 | 1 | 0 | 时钟空闲时为高电平,数据在下降沿采样,上升沿输出。 |

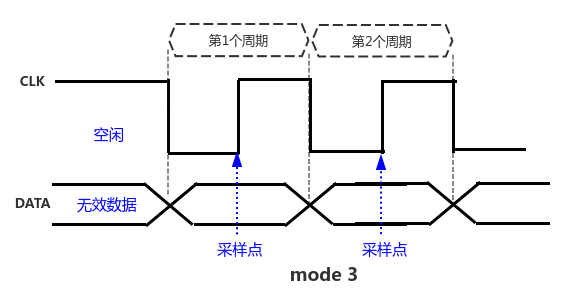

3 | 1 | 1 | 时钟空闲时为高电平,数据在上升沿采样,下降沿输出。 |

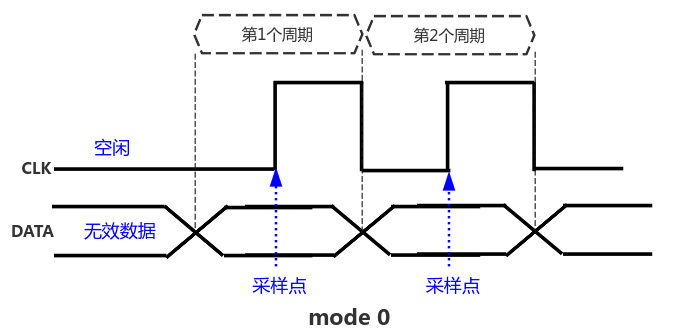

模式0 (CPOL=0; CPHA=0)

特性:

效果图:

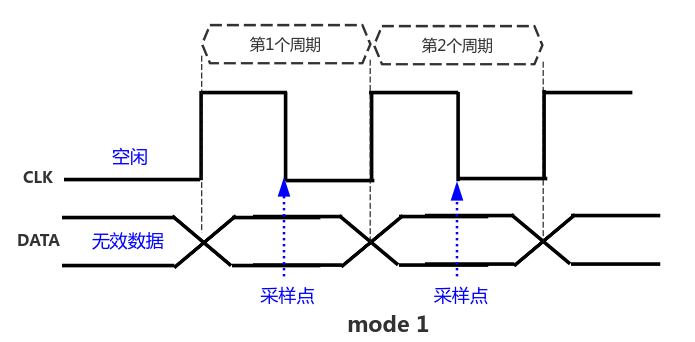

模式1 (CPOL=0; CPHA=1)

特性:

效果图:

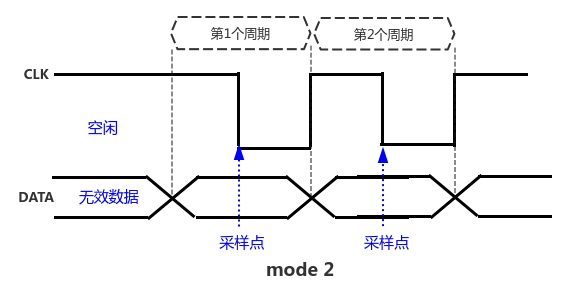

模式2 (CPOL=1; CPHA=0)

特性:

效果图:

模式3 (CPOL=1; CPHA=1)

特性:

效果图:

Modelsim的注意

写完源代码,一定要 ctrl+s 保存!!!

写完测试代码,也要 ctrl+s 保存!!!

否则,等会儿就算编译通过了,你的库(work)仍然是(empty)!!!